研究背景

近年来,二维(2D)材料以其在单原子厚度下优异的电学、光学和机械性能引起了广泛关注。然而,尽管已经做出了广泛的努力,但缺乏可扩展的方法来制备高质量的单层仍然是一个关键的挑战。以前实现2D单层的方法通常受到材料质量和可扩展性之间权衡的限制。其中,机械剥离方法可以获得最高质量的单层,大大加快了2D研究的快速进展,因此已被广泛用于最先进的器件演示。然而,剥离的薄片尺寸通常在几十微米的量级,并且产率非常低。因此,机械剥离大尺寸且高质量2D单层的简便方法对于加速基础研究以及潜在的商业化概念验证器件至关重要。

成果介绍

有鉴于此,近日,湖南大学刘渊教授团队通过设计原子级平坦的Au网格薄膜作为剥离胶带,报道了一种简单的机械剥离方法来制备大面积且高质量的2D半导体。使用预制的网孔胶带,有限的接触区域(2D晶体和Au之间)可以提供足够的粘附力以机械剥离均匀的2D单层,而非接触区域(网孔和单层之间)确保弱相互作用以机械释放2D单层到所需的衬底上。基于此,本文展示了一种可扩展的方法,可在不涉及任何溶液或污染的情况下将各种2D单层阵列干法剥离到不同的衬底上,实现了材料产率、可扩展性和质量之间的优化。此外,还进行了详细的光学和电学表征以确认其本征质量。凭借机械剥离各种2D阵列并进一步重新堆垛它们的能力,通过层对层组装展示了大面积的范德华异质结阵列。本文的研究提供了一种简单且可扩展的方法,用于干法剥离具有本征材料质量的2D单层和异质结阵列,这对于加速概念验证器件的基础研究和实际应用至关重要。文章以“Dry Exfoliation of Large-Area 2D Monolayerand Heterostructure Arrays”为题发表在顶级期刊ACS Nano上。

图文导读

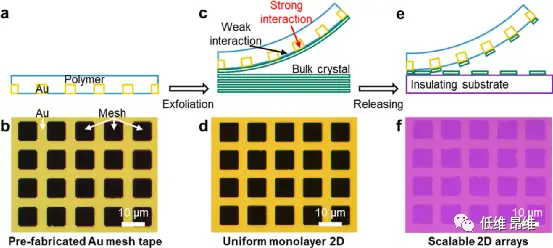

图1. 可扩展剥离过程的示意图和光学图像。(a&b)预制Au网孔胶带的示意图和光学图像。(c)机械剥离过程的示意图,其中部分接触区域可以提供足够的粘附力以机械剥离连续且均匀的单层MoS2。(d)Au网孔胶带上单层MoS2的相应光学图像。(e)机械释放过程的示意图。(f)PVA功能化的SiO2衬底顶部单层MoS2阵列的相应光学图像。

图1显示了可扩展剥离方法的制造过程。首先,使用标准光刻和热蒸发在牺牲硅衬底上预制Au网格薄膜(50 nm厚)。每个网格的尺寸为8×8 μm2,间距为3 μm,如图1a和b所示。然后,通过旋涂4 μm厚的聚(双酚A型碳酸酯)(PC)聚合物层作为支撑衬底,从硅衬底上机械剥离Au网格薄膜,从而能够制造Au网孔胶带。接下来,将Au网孔胶带直接压印在块材MoS2晶体的顶部,其中有限的接触区域(MoS2晶体和Au之间)仍然可以提供足够的粘附力以机械剥离连续且均匀的单层MoS2,如图1c和d所示。由此产生的单层MoS2尺寸可以达到厘米级,并最终受到块材晶体尺寸或结晶度的限制。为了转移单层MoS2,将带有单层MoS2的Au网孔胶带压在PVA功能化的300 nm SiO2/Si衬底上。通过相对较弱的相互作用,网孔顶部的MoS2可以很容易地释放到衬底上,如图1c和e所示。剥离Au网孔胶带后,与Au接触的单层MoS2也将被剥离,形成可扩展的单层MoS2阵列(图1f),其中阵列显示与预制Au网孔胶带相同的形状、周期和密度。与之前的方法相比,该方法不涉及任何刻蚀Au的溶液过程,因此,它可以保持精细2D晶格的本征性质。

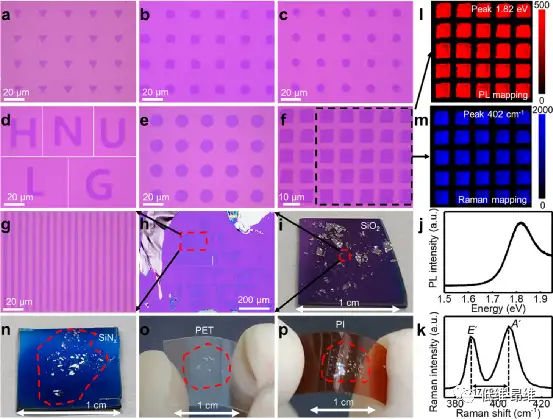

图2. 具有各种形状和在不同衬底上的可扩展MoS2阵列。(a-g)不同形状和间距的单层MoS2阵列的光学图像。(h&i)PVA功能化的SiO2衬底上大面积单层MoS2阵列的缩小光学图像和照片,其中在单层阵列周围观察到随机块材晶体。(j&k)剥离的单层MoS2阵列的PL和拉曼光谱,表明其单层性质。(l&m)单层MoS2阵列的PL和拉曼强度成像。(n-p)PVA功能化的SiNx衬底、透明PET衬底和柔性PI衬底上大面积单层MoS2阵列的照片。

通过预先设计不同的网孔结构,可以实现具有所需形状、周期和间距的各种MoS2阵列。如图2a-g所示,在PVA功能化的SiO2衬底上成功剥离了具有三角形、正方形、六边形、长方形、圆形和字母的单层MoS2阵列。对于矩形晶体,尺寸可以进一步增加到100 μm以上(图2g),只要矩形的短边在15 μm以下以保证足够的粘附力。注意到,由于块材晶体的不均匀性或潜在的缺陷位点(图2g-i),一些块材随机分布在单层阵列周围,类似于以前的湿法刻蚀剥离方法。光致发光(PL)光谱在1.82 eV(图2j)处有一个明显的峰,拉曼光谱的E'峰(面内振动)和A'峰(面外振动)之间的频率差为17.7 cm-1(图2k),表明剥离的MoS2阵列的直接带隙和单层性质。此外,进行了PL和拉曼成像,证明了均匀的强度,表明剥离的样品不仅在每个薄片内而且在阵列之间都是均匀的(图2l和m)。除了传统的SiO2之外,单层MoS2阵列也可以很容易地在其他衬底(如SiNx、PET或PI)上剥离,衬底顶部薄的PVA功能化层用于增强粘附力,如图2n-p所示。

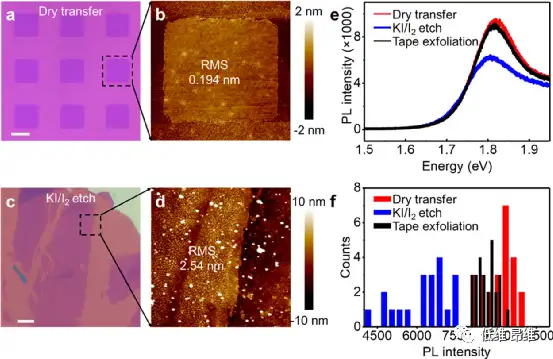

图3. 通过干法和湿法剥离的MoS2的AFM和PL表征。(a&b)干法剥离样品的AFM测量,展示了干净且原始的表面,RMS粗糙度为0.194 nm。(c&d)溶液刻蚀样品的AFM测量,RMS粗糙度为2.54 nm,表明刻蚀过程会留下不可避免的残留物。(e&f)通过不同方法获得的单层MoS2的PL光谱。

该方法的主要优势之一是干法剥离和干法释放过程,无需任何溶液,因此它可以保持2D晶格的本征性质。为了进行比较,还使用传统的Au薄膜剥离制备了另一个样品,将其转移到相同的PVA功能化衬底上,然后进行KI/I2溶液刻蚀。如图3a和b所示,干法剥离的MoS2显示出清洁且原始的表面,均方根(RMS)粗糙度为0.194 nm,表明使用干法剥离优化了表面。相比之下,溶液刻蚀的样品在MoS2顶部显示杂质,RMS达到2.54 nm(图3c和d),表明刻蚀过程会留下不可避免的残留物。通过对干法剥离样品和刻蚀样品进行PL测量,可以进一步证实样品质量的提高。如图3e所示,干法剥离的样品表现出9500计数的更高PL强度,并且与透明胶带方法剥离的单层样品相当。相比之下,溶液刻蚀的样品显示PL强度大大降低,范围从4300到7500,表明MoS2的本征特性受到Au刻蚀工艺的影响。除了PL强度之外,刻蚀样品中的PL峰也从1.820 eV移动到1.805 eV,这可能归因于刻蚀过程中产生的张力应变。

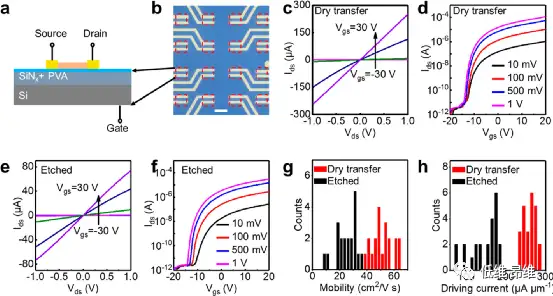

图4. 单层MoS2阵列的电学特性。(a&b)背栅单层MoS2晶体管阵列的示意图和光学图像。(c&d)干法剥离的单层MoS2器件的输出和转移曲线,展示出欧姆接触、108的开/关比和63 cm2/V s的载流子迁移率。(e&f)对照器件的输出和转移曲线(从Au薄膜剥离,然后进行KI/I2蚀刻)。(g&h)超过20个晶体管的载流子迁移率和驱动电流统计分布。

由于能够在绝缘衬底上干法剥离大面积MoS2阵列,可以直接制备晶体管阵列,而无需对连续单层样品(CVD合成或机械剥离制备)进行额外的图案化过程,因此,可以避免传统图案化工艺引起的污染。如图4a和b所示,20/30 nm厚的Ag/Au用作源-漏电极,高掺杂硅作为背栅,80 nm/18 nm SiNx/PVA用作栅极电介质。如图4c所示,Ids-Vds输出特性显示出线性行为,表明金属和单层MoS2之间存在欧姆接触。随着Vds增加超过2 V,Ids电流逐渐饱和,达到的最高驱动电流为280 μA/μm。图4d显示了相应器件的Ids-Vgs转移特性,其中观察到明显的n型行为和超过108的开/关比。此外,可以从跨导中提取出63 cm2/V s的两端场效应迁移率。注意到,驱动电流和载流子迁移率与没有复杂接触或顶栅结构的单层MoS2的最佳值相当,表明使用干法剥离优化了材料和器件性能。为了进一步证明干法剥离方法的重要性,还制备了MoS2晶体管(具有相同的PVA/SiNx背栅电介质),其中MoS2沟道通过湿法KI/I2溶液刻蚀工艺剥离(图4e和f)。如图4g和h所示,刻蚀样品表现出较低的载流子迁移率,10~35 cm2/V s,不到干法剥离样品(40~63 cm2/V s)的一半。重要的是,驱动电流也显示出较低的值,70~183 μA/μm,这也是干法剥离样品(234~280 μA/μm)的一半左右,这主要归因于接触和沟道区域内不可避免的残留物。更窄的电流分布可能源于无残留和均匀的表面条件,这对于实际应用很重要。

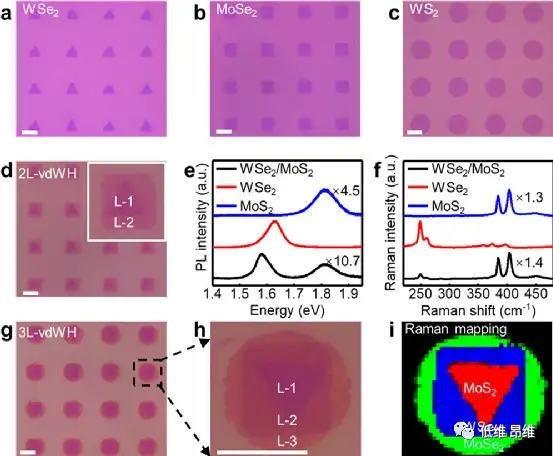

图5. 各种2D材料和异质结阵列的光学图像和表征。(a-c)单层WSe2阵列、MoSe2阵列和WS2阵列的光学图像。(d-f)两层WSe2/MoS2 vdWH阵列的表征。(g-i)MoSe2/WSe2/MoS2三层vdWH阵列的光学图像和拉曼成像。

这种简单的机械剥离方法不仅限于MoS2,还可以扩展到其他2D材料,其中Au网孔胶带可以形成强大的粘附力。为了证明这一点,应用这种方法来剥离单层WSe2阵列、单层MoSe2阵列和单层WS2阵列,如图5a-c所示。凭借原始表面和高可扩展性,剥离的2D材料阵列可进一步用于构建大面积vdW异质结阵列。如图5d所示,剥离的WSe2阵列使用对准转移技术集成在干法剥离的MoS2阵列顶部,形成具有设计形状和结构的可扩展vdWH阵列。图5e显示了双层MoS2/WSe2 vdWH的PL光谱,在1.57 eV处产生清晰的层间激子,与之前的报道一致,并表明可扩展干法剥离过程具有原始的界面。此外,如三层MoSe2/WSe2/MoS2 vdWH阵列(图5g-i)所示,更复杂的vdWH阵列可以通过反复逐层集成干法剥离的2D阵列来制备。在该方法中,可以大规模剥离和集成具有本征特性的复杂vdWH阵列,因此,可以大大加快vdWH的基础研究和实际应用。

总结与展望

本文报道了一种用设计的Au网孔胶带代替传统透明胶带的简单剥离方法。使用这种方法,可以在不同衬底上剥离各种2D单层阵列,而不涉及任何溶液和污染,克服了之前材料产率、可扩展性和质量之间的权衡。进行了不同的表征方法(AFM、拉曼、PL、光学和电学测量)来证明剥离单层的本征性质。重要的是,可以进一步逐层集成具有不同形状和组合的大面积vdWH阵列,同时保持其原始界面质量。这种简单且可扩展的剥离方法对于加速概念验证器件的基础研究和实际应用至关重要。

文献信息

Dry Exfoliation of Large-Area 2D Monolayer and Heterostructure Arrays

(ACS Nano, 2020, DOI:10.1021/acsnano.1c05734)

文献链接:https://pubs.acs.org/doi/10.1021/acsnano.1c05734

原文刊载于【低维 昂维】公众号

本文版权归原作者所有,文章内容不代表平台观点或立场。如有关于文章内容、版权或其他问题请与我方联系,我方将在核实情况后对相关内容做删除或保留处理!