随着人工智能时代的来临,基于传统的冯诺伊曼构架的运算系统对大数据的处理表现出有限的计算速度和庞大的能量损耗。这主要是由冯诺伊曼构架中运算与存储单元的分离和二者运行速度的不匹配所导致。因此大量的能量在数据的传输中被损耗掉,同时也降低了运算效率。在人脑运算系统的启发下,类脑运算逐渐在复杂的学习,识别,和存储中表现出高运算速度,低能量损耗与一定的容错率等优势,所以被认为有望缓解如今的计算瓶颈。在类脑运算系统中, 人工突触在神经元之间的信息传递中起着极为关键的作用。同时,基于两端忆阻器的大量研究工作已致力于模拟突触在神经网络中的作用。两端忆阻器由于结构简单,开关电压低,所以具有易集成,能耗低等优势。但结构简单的两端忆阻器在突触权重需要不断矫正更新的持续读写过程中表现出不稳定性的特性。

三端突触器件具有完全独立的端口来进行读写操作,很大程度上可以缓解重复读写过程中的不稳定性问题。三端突触器件的原理主要基于电荷在浮栅,界面陷阱态,电介质缺陷态中的存储机制来实现可控的突触权重更新。此外,基于二维范德瓦尔斯异质结的三端器件在非挥发电学和光电存储器中也已有了广泛的应用。尤其是近期一篇关于大面积二硫化钼浮栅场效应晶体管实现复杂的逻辑存储一体化计算功能的研究更加预实着大面积集成三端器件的前景。但是三端器件的高操作电压一直限制其在低功耗存储和人工突触方面的应用。虽然通过使用机械剥离或者原子层沉积方式获得的高介电常数电介质作为浮栅器件中的控制栅极可以缓解高操作电压的问题,但CMOS兼容性与漏电隐患也会随之产生。而通过转移具有不同特性或者能带适配的二维材料所形成的范德华异质结已经表现出新奇的性质与独特的功能。

受此启发,新加坡国立大学陈伟教授团队通过选择能带适配的二维材料来制备范德瓦尔斯异质结,并探索了其在低功耗存储器件及人工突触器件中的应用。异质结器件主要由多层石墨烯(FLG),氮化硼(h-BN)和二硫化锡(SnS2)组成。因为SnS2具有较大的电子亲合能(~4.8 eV)和能带宽度(~2.2 eV),当其与h-BN相结合时,会形成不对称的电荷注入势垒,使得空穴更易于穿过势垒注入多层FLG中。凭借着空穴在多层石墨烯中的捕获和脱陷过程,浮栅器件表现出了优异的存储特性,例如高电流开关比(105),长电流保持时间(104s), 和稳健的循环耐受性(1000 次开关循环)。得益于较小的空穴注入势垒,多级存储态也可在小于10 V的操作电压下实现。将浮栅器件进一步应用于人工突触器件,它成功地模拟了突触的多种功能,例如EPSC/IPSC, PPF, SRDP, LTP/LDP。该突触器件在LTP/LTD过程中表现出的优异的线性度与高开关电导比使其在MNIST手写数据集上表现出90%的高识别精度。LTP/LTD在不同循环和器件间表现出的一致性更预示了此三端器件在复杂神经网络中应用的前景。

该工作在InfoMat上以题为“Band-tailored van der Waals heterostructure for multilevel memory and artificial synapse”在线发表(DOI:10.1002/inf2.12230)。

我们摘取了文章里的几部分重点给大家做个介绍:

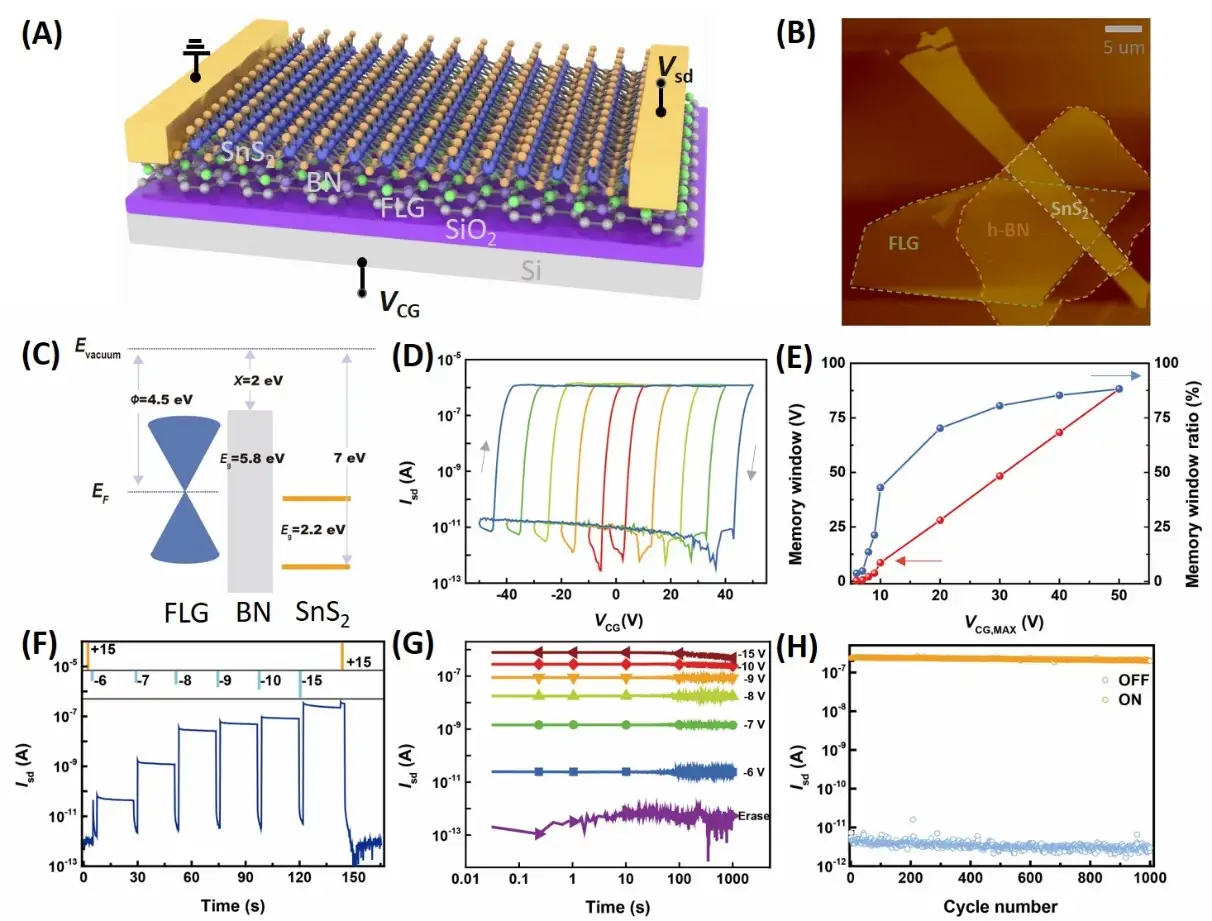

1.异质结的表征与存储器件的多级存储行为

图1A的器件结构图显示了浮栅器件主要由FLG,h-BN和SnS2构成。从AFM的表征结果中可看出制备的异质结具有很高的品质(图1B)。图1C是异质结的平带能带图。因为SnS2具有较大的功函数(~5.1 eV)和价带顶(~7 eV),因此SnS2和h-BN间可形成较低的空穴注入势垒,从而有利于降低器件的高操作电压问题。在电测量过程中,电压VCG施加到具有300 nm SiO2的硅片底部,同时测试通过SnS2沟道的源漏电流(Isd)。图1D是器件的转移特性曲线,滞回曲线显示出器件具有存储特性。同时,存储窗口随着电压VCG扫描范围的扩展而逐渐增大,在VCG大于30 V时达到80 %的占比(图1E)。此外通过调节操作电压,器件可实现多级存储功能(图1F),并且得益较小的空穴注入势垒,多级存储可在小于10 V的操作电压下实现。在对多级存储态进行电流保持时间与循环耐久性测试时,器件表现出很好的长期存储能力和极强的稳健性(图1G和1H)。

图1 范德瓦尔斯器件的表征及其多级存储性质

2.异质结浮栅器件的工作机理

为了探究浮栅存储器的工作机制,通过异质结的纵向电流被测试收集并用来进一步分析电荷输运过程。图2A显示出通过异质结的输运电流在小电压下缓慢增长,大电压下急速增长的行为。这一现象表明在不同的电压范围内电荷输运机制有所不同。在Vb小于阈值电压(Vth)时(图2B),纵向电流值(lnI)与Vb1/2表现出基于Richardson-Schottky模型的正线性关系,所以在此区域空穴的注入主要基于热电子发射机理。而当Vb大于Vth时,空穴的注入则依赖于Fowler-Nordheim隧穿,这一机理可由在图2C中大电压下的FN负线性拟合所证实。图2D中的能带图进一步形象地揭示了电荷注入机制,在Vb小于Vth时,空穴在热激发的协助下穿过异质结的梯形势垒,而当Vb持续增大到大于Vth时,梯形势垒会在大电压下转变为较窄的三角形势垒,三角形势垒有利于空穴通过FN隧穿的方式注入,促使电流快速增长。考虑到器件可在较小的操作电压下实现多级存储,所以空穴的注入主要依赖于热激发模式。从存储电流与操作电压和温度的依赖关系(图2E)可看出,在室温附近存储电流与测试温度有着较强的依赖关系,在进一步排除半导体电导随温度增长的特性后,可得出此存储器的工作原理主要基于热激发所导致的空穴注入浮栅被其捕获后所形成的屏蔽场对沟道电流造成了滞回影响。

图2 浮栅存储器件工作原理

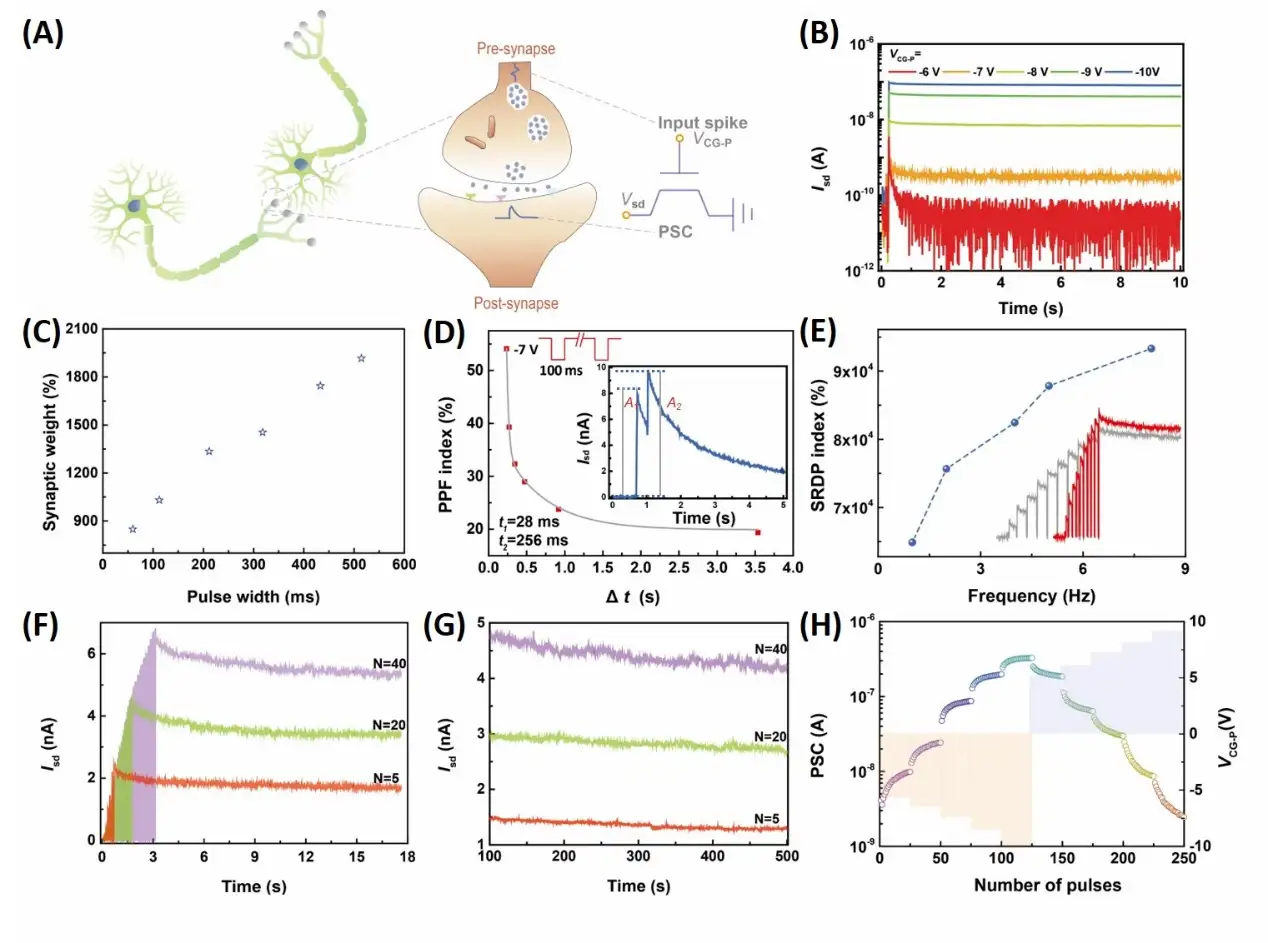

3.浮栅器件模拟人工突触行为

具有多级存储的浮栅器件可进一步被用来模拟人工突触行为。在此器件中,来自底栅极的电脉冲可作为输入脉冲来调制半导体SnS2中的突触后电流(PSC)。图3B是器件对具有不同强度输入电脉冲的激发性突触后电流响应(EPSC)的时间演变曲线,从中可以看出随着脉冲强度的增大,激发的电流不能回到初始值,揭示了长时程突触可塑性行为(long-term plasticity behavior)。激发性突触后电流响应也可由电脉冲宽度来控制(图3C),所计算的突触权重随着电脉冲宽度线性增长,表明了在更大的电脉冲宽度下可捕获更多的空穴。由于捕获空穴的过程可在小的操作电压下实现,因此器件具有低功耗的优势。该浮栅器件还可模拟双脉冲易化(PPF)行为(图3D),通过用双指数函数对PPF指数与两脉冲间隔时长进行拟合,所得出的时间常数(t1=28 ms,t2=256 ms)也与生物学上的数值相吻合。此外,具有更高频率和更多数量的电脉冲也可刺激产生更加强烈的突触响应,且响应电流随时间的演变逐步稳定在了非初始值(图3E,F和G),这些行为成功模拟了生物学上短时程至长时程生物可塑性的转变过程(short term to long-term plasticity transition)。在图3H中,通过施加一系列不同强度的电脉冲,突触后电流表现出逐步的增加和减小的特性,表明模拟器件具有很强的突触调制性。

图3 人工突触行为的模拟

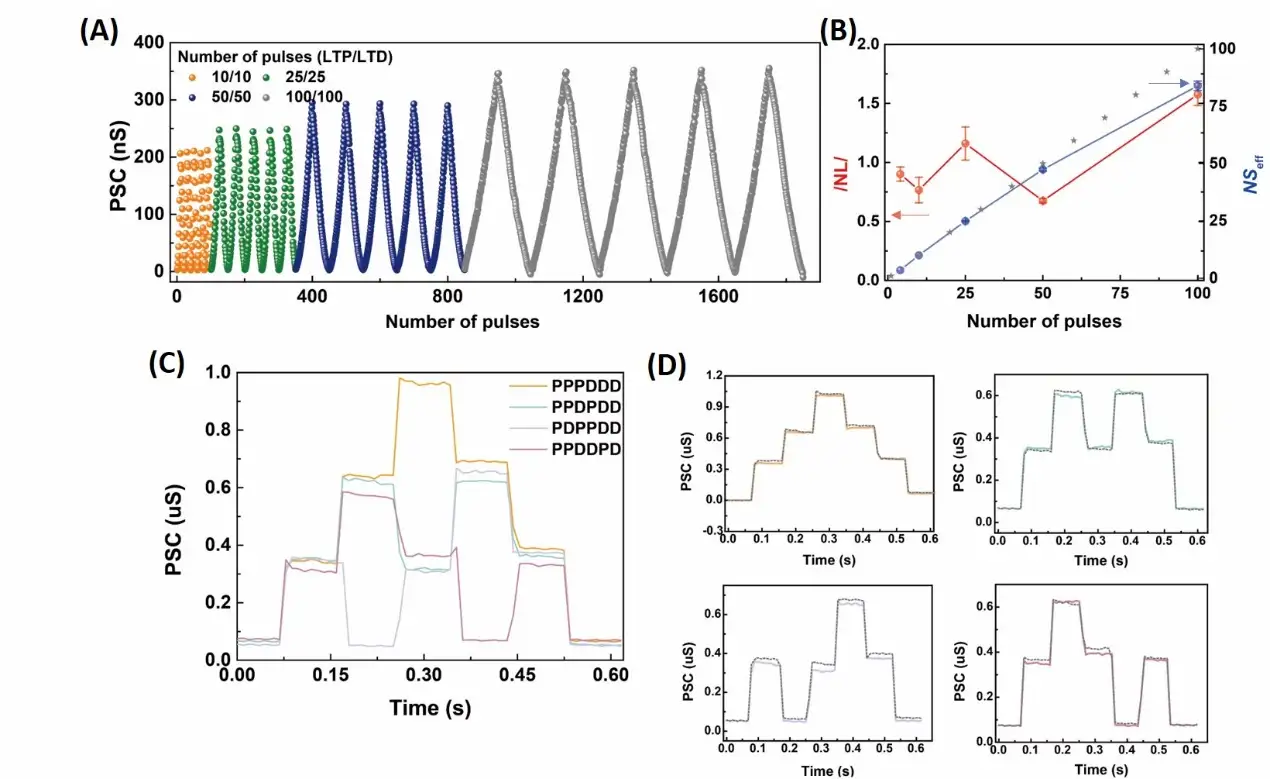

4.人工突触器件的操作稳定性

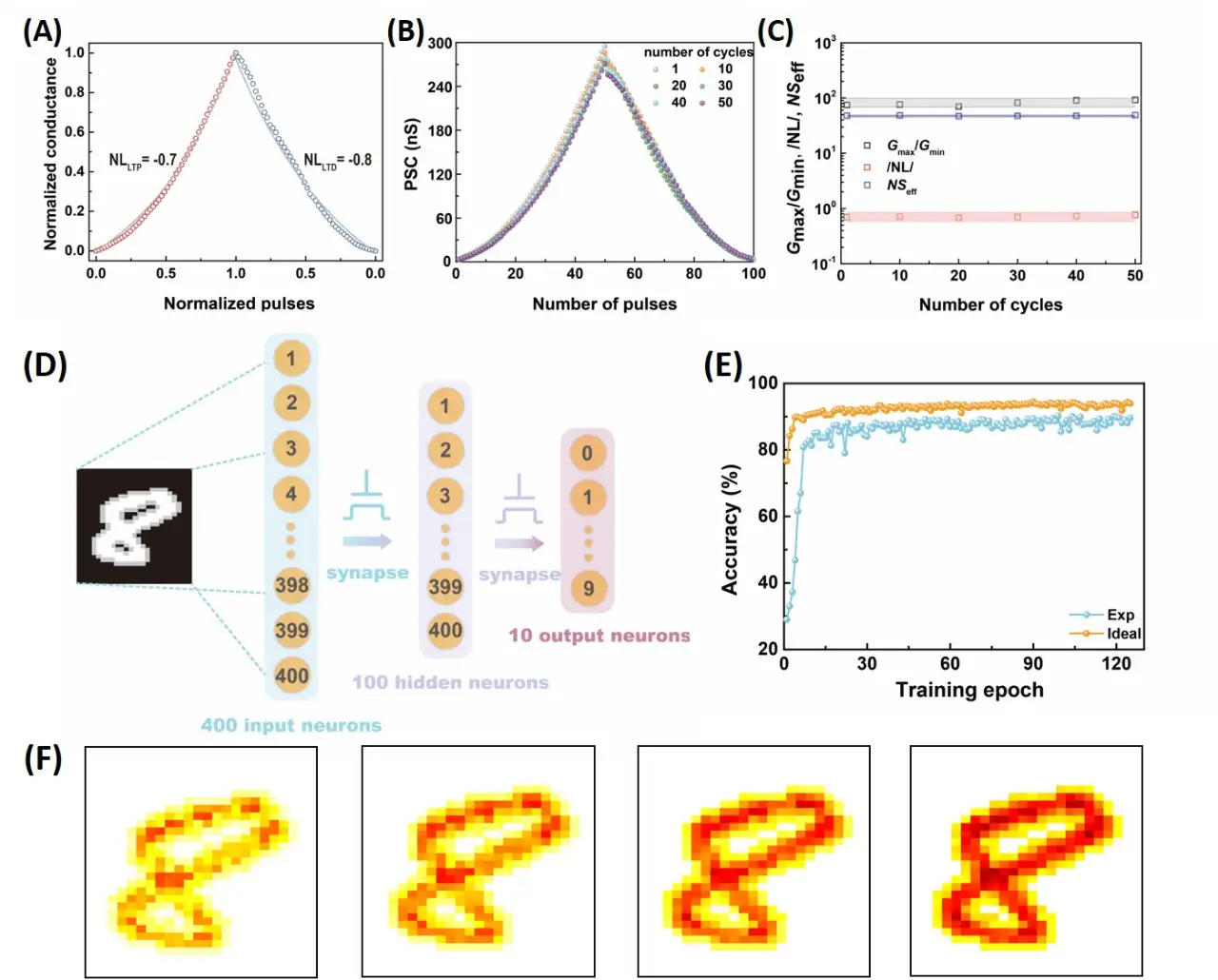

长时程增强/抑制效应(LTP/LTP)过程中电导的线性调制,高开关电导比和多级存储态,以及电导的低循环和低器件差异性均是在人工神经网络中实现高识别精度的关键。图4A是突触器件在不同数量电脉冲下循环测试的LTP/LTD行为,其表现出很高的稳定性和可重复性。从图4B可看出,在不同数量电脉冲下,突触器件表现出优异的线性权重更新行为(线性度均小于2)和多的有效态数。同时器件对于不规则形式的电脉冲也表现出了稳定的权重更新行为(图4C和D)。不仅如此,器件在50次LTP/LTD的循环耐受力的表现中展现了小的循环差异性(8%)(图五B)。且其众多性能,例如线性度(<1),开关电导比(~80),有效态数(~47)均维持在优异且稳定的范围(图5C)。正因突触器件在LTP/LTD中展现的优异且稳定的性能从而使得其在全连通人工神经网络MNIST手写数据集的模拟中展现出了90%的高识别精度(图5D和E)。

图4 人工突触器件的工作稳定性

图5 突触器件在人工神经网络中的图像识别应用

5.结论

通过能带调节,本工作报导了基于FLG/h-BN/SnS2的三端浮栅器件。SnS2和h-BN材料的选择使得SnS2和FLG间形成了小的空穴注入势垒。基于此,浮栅器件可在小的操作电压(<10 V)下工作。且其展现的多级存储也表现出较长的保留时间与好的循环耐受性。该浮栅器件也可用来模拟神经突触行为。由于较小的操作电压,该人工突触器件的能耗也降低至皮焦量级。此外器件在LTP/LTD测试中所表现出的高线性度和开关电导比更促使此器件在人工神经网络的模拟中实现了90%的高识别精度。这些结果预示着此三端器件有望应用于高能效的神经计算系统中。

原文刊载于【InfoMat】公众号

本文版权归原作者所有,文章内容不代表平台观点或立场。如有关于文章内容、版权或其他问题请与我方联系,我方将在核实情况后对相关内容做删除或保留处理!